ERAI Executive Conference San Diego, Calif April 22 - 23, 2015

Risk Mitigation of Sophisticated Counterfeit ICs Using Cost Effective Electrical Testing Techniques

# Sultan Ali Lilani

Technical Support Integra Technologies LLC 3450 N Rock Road, Building 100 Wichita, Kansas 67226

Ph 510-830-9216 Email: sultan.lilani@Integra-tech.com Web: www.integra-tech.com

## Outline

- 1. Devices keep getting more complex.

- 2. The counterfeit problem is not going away anytime soon.

- 3. Complex devices are being more frequently counterfeited.

- 4. Traditional counterfeit detection techniques are no longer adequate to identify complex counterfeits.

- 5. Full AC/DC/Functional at speed electrical test over the rated temperature is the best defense.

- 6. What do AC, DC and Functional testing mean?

- 7. Example complex device test development costs.

- 8. Ways to reduce the cost complex device testing.

- 9. Steps to follow to assure testing is performed to meet your needs.

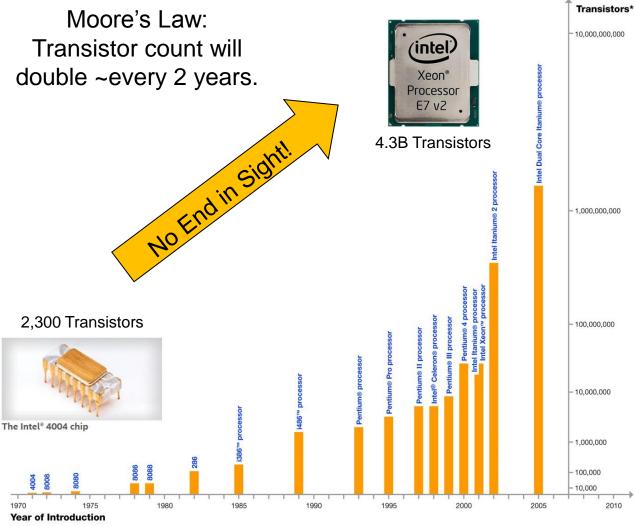

## **Devices keep getting more complex!**

Some may argue that Moore's law is beginning to slow down, but with the advent of 2.5 and 3D packaging, there is no realistic future limit to how many transistors can be in a "device."

\*Note: Vertical scale of chart not proportional to actual Transistor count.

Source: Intel Corporation

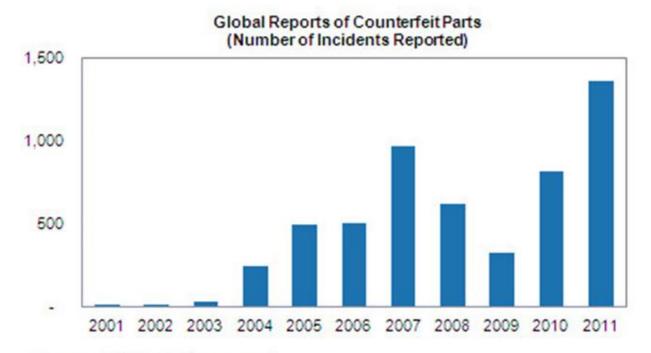

## The Counterfeit problem continues to grow

Source: IHS Parts Management

Figures represent ERAI Suspect Counterfeit or High Risk Part Incidents and GIDEP Suspect Counterfeit Alerts for electronic components

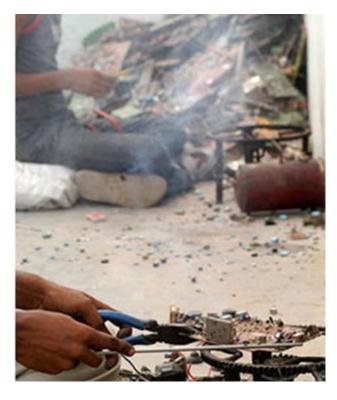

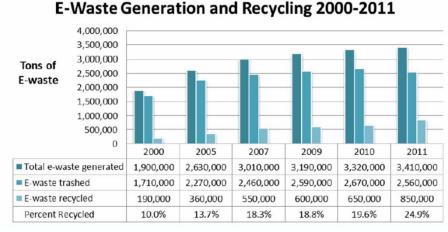

## **Counterfeit devices are getting more sophisticated**

- 1. More products are being recycled creating more opportunity for reclaimed parts.

- 2. Newer recycled products contain more complex devices than older products.

- 3. Remarked counterfeit devices are nearly indistinguishable from authentic ones.

- 4. Redesigned clones of simple devices are appearing complex devices are next.

#### Source: electronicstakeback.com and the EPA

# What can be done to eliminate counterfeit parts?

- 1. Buy parts from the original manufacturer or authorized distributor whenever possible (Xilinx, Avnet, Arrow).

- 2. Buy parts from authorized after market manufacturers (Traditionally companies like Rochester and Lansdale, but increasingly companies like Avnet and Arrow).

- 3. Buy parts from known sources with original paperwork traceable to the original manufacturer (another OEM that bought parts from a franchised source and has the original paperwork).

- 4. Do last time buys when parts become obsolete (can be expensive and hard to estimate exactly how many will be needed).

- 5. Qualify alternative suppliers which may not yet be obsolete (when market demand decreases usually all suppliers get out of the market).

- 6. Use FPGA's/ASICs to emulate obsolete devices (expensive, requires board re-layout at a minimum).

- 7. Redesign systems to use non-obsolete parts (most expensive option).

- 8. Buy parts from a reputable non-franchised broker (risk based testing and evaluation is necessary).

- 9. Buy parts from a questionable broker (must do full electrical test and possibly qualification).

# What can be done to eliminate counterfeit parts?

- 1. Buy parts from the original manufacturer or authorized distributor whenever possible (Xilinx, Avnet, Arrow).

- 2. Buy parts from authorized after market manufacturers (Traditionally companies like Rochester and Lansdale, but increasingly companies like Avnet and Arrow).

- 3. Buy parts from known sources with original paperwork traceable to the original manufacturer (another OEM that bought parts from a franchised source and has the original paperwork).

- 4. Do last time buys when parts become obsolete (can be expensive and hard to estimate exactly how many will be needed).

- 5. Qualify alternative suppliers which may not yet be obsolete (when market demand decreases usually all suppliers get out of the market).

- 6. Use FPGA's/ASICs to emulate obsolete devices (expensive, requires board re-layout at a minimum).

- 7. Redesign systems to use non-obsolete parts (most expensive option).

- Buy parts from a reputable non-franchised broker (risk based electrical testing and evaluation is necessary).

- Buy parts from a questionable broker (must do full electrical test and possibly qualification).

## What do you do when you must buy suspect parts?

As counterfeiters become more sophisticated, full AC/DC/Functional at speed electrical testing is becoming essential.

|             |                        |                                    |                                     |        |           | Dete                        | ction              | Metho            | ods                     |                                |                |

|-------------|------------------------|------------------------------------|-------------------------------------|--------|-----------|-----------------------------|--------------------|------------------|-------------------------|--------------------------------|----------------|

|             |                        |                                    | External<br>Visual &<br>Phys<br>Dim | XRF    | X-<br>Ray | Marking<br>Perm<br>Blacktop | Internal<br>Visual | Basic<br>DC Test | Min<br>Func<br>Test 25C | Full Spec<br>Extended<br>Temps | Test &<br>Qual |

|             | Non                    | No Die                             | Possible                            | No     | Yes       | Possible                    | Yes                | Yes              | Yes                     | Yes                            | Yes            |

|             | Functioning<br>Devices | Wrong Die<br>Re-Marked             | Possible                            | No     | Likely    | Possible                    | Likely             | Yes              | Yes                     | Yes                            | Yes            |

|             |                        | Failed Real<br>Parts               | No                                  | No     | No        | No                          | No                 | Possible         | Likely                  | Yes                            | Yes            |

| Type        |                        | Pulls<br>Refurbished               | Possible                            | Likely | No        | No                          | No                 | Possible         | Possib e                | Possible                       | Yes            |

|             |                        | Speed /spec<br>&temp<br>up-marking | Possible                            | No     | No        | Possible                    | No                 | No               | Possible                | Yes                            | Likely         |

| Counterfeit | Functioning<br>Devices | Recovered<br>Die                   | No                                  | No     | No        | No                          | Possible           | No               | Possible                | Possible                       | Likely         |

| ပိ          |                        | Similar/<br>Substitution           | Possible                            | No     | No        | Possible                    | Possible           | No               | Possible                | Yes                            | Likely         |

|             |                        | Pb Free<br>Re-marked               | Possible                            | Yes    | No        | Possible                    | No                 | No               | No                      | No                             | No             |

|             |                        | Lesser part<br>(knock-off)         | Possible                            | No     | No        | Possible                    | Possible           | Possible         | Possible                | Likely                         | Yes            |

TECHNOLOGIES

## **Standard Counterfeit Test Approaches**

- 1. Paperwork Inspection (if any exists).

- 2. Gross Visual Inspection Bent leads, package cracks, etc.

- 3. Fine Visual Inspection evidence of remarking, lead contamination.

- 4. Remark/Resurface solvent testing

- 5. X-Ray Is there a die in the package, do al the die look the same.

- 6. XRF Are there any foreign elements present.

- 7. Decap Die verification, size marking, etc.

- 8. Curve Trace Not a true electrical test.

In the "cat and mouse" game with the counterfeiters, these mechanically oriented tests are no longer sufficient to catch complex counterfeit devices!

## Standard counterfeit tests will not catch these types of counterfeits:

- 1. Substitution of one speed device for another.

- 2. Substitution of one temperature grade device for another.

- 3. Substitution of one die revision for another.

- 4. Substitution of a low power device for a high power one & vice versa.

- 5. Cloned devices redesigned exact copies of the original device.

- 6. Parts with ESD or electrical overstress damage not confined to the periphery of the device.

- 7. Original parts stolen from the manufacturer could be passing or failing parts.

- 8. "Walking wounded" devices that have been mishandled in any number of ways that has caused performance degradation.

The only way to catch these types of counterfeit devices is to perform full DC, AC and Functional testing at full speed and over the full temperature range of the device.

## What do the original manufacturers do?

The manufacturer must test for every conceivable application and every manufacturing defect.

The manufacturers use sophisticated simulation tools to simulate the faults and use BIST, DFT etc. in order to make sure there are no manufacturing defects and that the device performs to its datasheet limits.

This is a time consuming and expensive job.....

Fortunately for us the manufacturers have already done this testing for us on every single device - and so we as users should never see any of these failures.

Unfortunately for us, the manufacturers do not allow any after-market sources to use their proprietary test programs – so our only choice is to intelligently develop that test capability ourselves.

**DC Testing** - DC testing is the first step, but it actually does very little to determine if a device is counterfeit.

**AC Testing** - is better than DC testing alone, but still can not tell you if a device is counterfeit.

Full DC, AC and Comprehensive Functional testing at Full Speed and over the Rated Temperature Range - is the only way to gain the greatest assurance that a device is not counterfeit.

We will explore each of these in more detail.

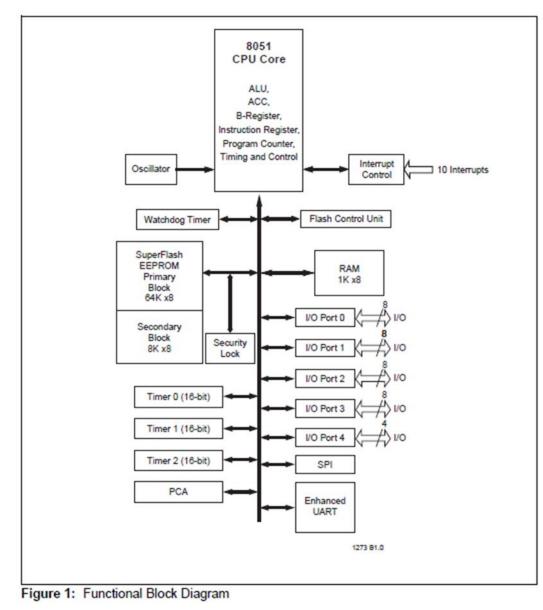

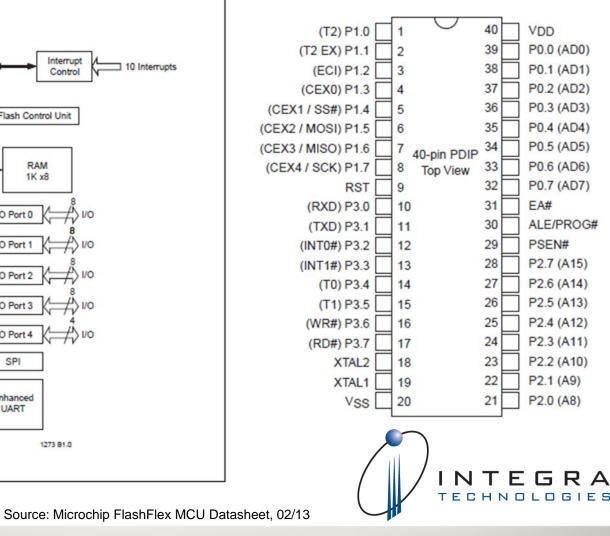

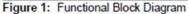

## The Example – Relatively Simple 8051 8-bit Microcontroller

Example Block Diagram and pin-out for a legacy 8051 device.

#### **DC Electrical Characteristics**

Table 36: DC Electrical Characteristics for SST89E516RDx  $T_A = -40^{\circ}$ C to +85°C; V<sub>DD</sub> = 4.5-5.5V; V<sub>SS</sub> = 0V

| Symbol           | Parameter                                                      | Test Conditions                               | Min                         | Max                         | Units |

|------------------|----------------------------------------------------------------|-----------------------------------------------|-----------------------------|-----------------------------|-------|

| VIL              | Input Low Voltage                                              | 4.5 < V <sub>DD</sub> < 5.5                   | -0.5                        | 0.2V <sub>DD</sub> -<br>0.1 | v     |

| VIH              | Input High Voltage                                             | 4.5 < V <sub>DD</sub> < 5.5                   | 0.2V <sub>DD</sub> +<br>0.9 | V <sub>DD</sub> + 0.5       | v     |

| VIH1             | Input High Voltage (XTAL1, RST)                                | 4.5 < V <sub>DD</sub> < 5.5                   | 0.7Vpp                      | V <sub>DD</sub> + 0.5       | v     |

| Vol              | Output Low Voltage (Ports 1.5, 1.6, 1.7)                       | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  |                                                                | IoL = 16mA                                    |                             | 1.0                         | V     |

| Vol              | Output Low Voltage (Ports 1, 2, 3) <sup>1</sup>                | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  |                                                                | loL = 100µA <sup>2</sup>                      |                             | 0.3                         | v     |

|                  |                                                                | IoL = 1.6mA <sup>2</sup>                      |                             | 0.45                        | V     |

|                  |                                                                | IoL = 3.5mA <sup>2</sup>                      |                             | 1.0                         | V     |

| VoL1             | Output Low Voltage (Port 0, ALE,                               | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  | PSEN#) <sup>1,3</sup>                                          | I <sub>OL</sub> = 200µA <sup>2</sup>          |                             | 0.3                         | V     |

|                  |                                                                | $I_{OL} = 3.2 m A^2$                          |                             | 0.45                        | V     |

| VOH              | Output High Voltage (Ports 1, 2, 3, ALE,                       | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  | PSEN#) <sup>4</sup>                                            | l <sub>OH</sub> = -10μA                       | V <sub>DD</sub> - 0.3       |                             | v     |

|                  |                                                                | I <sub>OH</sub> = -30µА                       | V <sub>DD</sub> - 0.7       |                             | v     |

|                  |                                                                | I <sub>OH</sub> = -60µА                       | V <sub>DD</sub> - 1.5       |                             | v     |

| VOH1             | Output High Voltage (Port 0 in External                        | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  | Bus Mode) <sup>4</sup>                                         | l <sub>OH</sub> = -200μA                      | V <sub>DD</sub> - 0.3       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -3.2mA                      | V <sub>DD</sub> - 0.7       |                             | v     |

| VBOD             | Brown-out Detection Voltage                                    |                                               | 3.85                        | 4.15                        | V     |

| կլ               | Logical 0 Input Current (Ports 1, 2, 3)                        | V <sub>IN</sub> = 0.4V                        |                             | -75                         | μA    |

| ITL              | Logical 1-to-0 Transition Current (Ports 1, 2, 3) <sup>5</sup> | V <sub>IN</sub> = 2V                          |                             | -650                        | μA    |

| lu -             | Input Leakage Current (Port 0)                                 | 0.45 < V <sub>IN</sub> < V <sub>DD</sub> -0.3 |                             | ±10                         | μA    |

| R <sub>RST</sub> | RST Pull-down Resistor                                         |                                               | 40                          | 225                         | KΩ    |

| CIO              | Pin Capacitance <sup>6</sup>                                   | @ 1 MHz, 25°C                                 |                             | 15                          | pF    |

| DD               | Power Supply Current                                           |                                               |                             |                             |       |

|                  | IAP Mode                                                       |                                               |                             |                             |       |

|                  | @ 40 MHz                                                       |                                               |                             | 88                          | mA    |

|                  | Active Mode                                                    |                                               |                             |                             |       |

|                  | @ 40 MHz                                                       |                                               |                             | 50                          | mA    |

|                  | Idle Mode                                                      |                                               |                             |                             |       |

|                  | @ 40 MHz                                                       |                                               |                             | 42                          | mA    |

|                  | Power-down Mode (min. VDD = 2V)                                | T <sub>A</sub> = 0°C to +70°C                 |                             | 80                          | μA    |

|                  |                                                                | T <sub>A</sub> = -40°C to +85°C               |                             | 90                          | μA    |

#### Source: Microchip FlashFlex MCU Datasheet, 02/13

## **Example DC Parametrics Table:**

This DC table looks very similar to every DC table in nearly any datasheet, regardless of the device functionality.

- The DC parametrics listed in the device datasheet only represent voltage and current limits used by the device to interface it to other circuitry on a PCB.

- It also includes measuring the operating current.

- It has almost nothing to do with how the device functions.

- For instance, If you compare the DC parametrics for an Analog to Digital Converter to an a DDR3 Dynamic Ram, they look very similar, however the functionality of the devices could hardly be more different.

- DC testing only evaluates a very small percentage of the transistors along the periphery of the die.

## What is DC Testing?

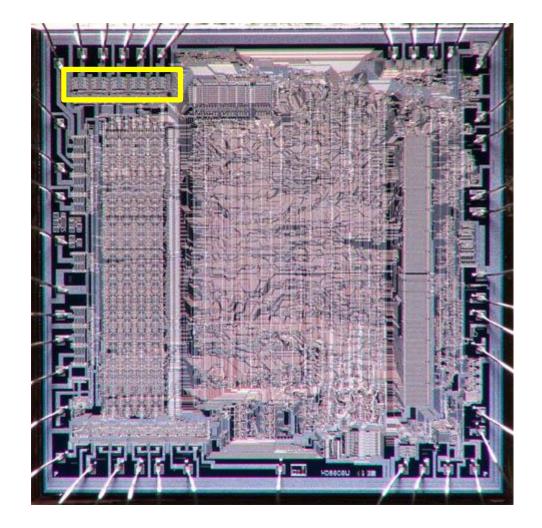

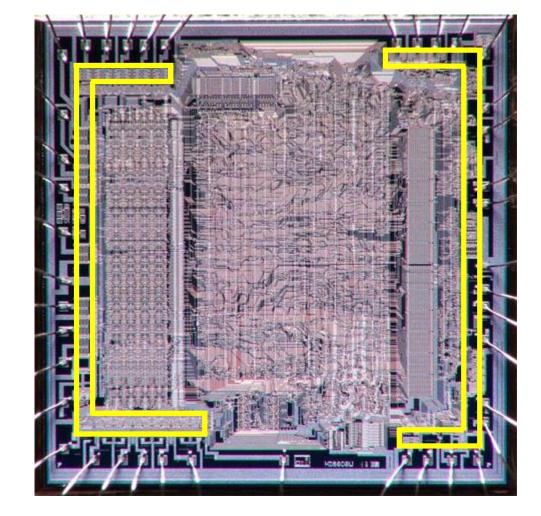

DC testing only covers the yellow circled part of the die –

Generally the first few transistors and the input diode at the entry point of the main circuitry.

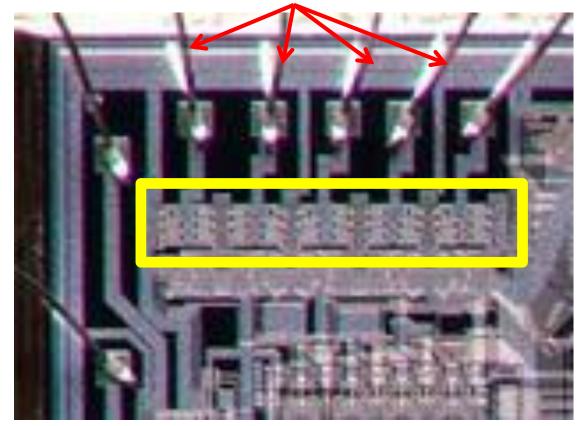

## What is DC Testing?

Bond wires to the leadframe and then to the external device pins

**Enlarged Picture**

DC testing only covers the circuitry enclosed in the yellow square -Essentially the first few transistors of each pin of the device.

## What is DC Testing?

The yellow portion is and estimate of the circuitry that might be tested by DC only testing - in fact it is likely a substantial overestimate of the actual circuitry being tested with DC tests.

## What can DC testing tell you?

- If an individual pin has been damaged by Electrical Over Stress (EOS) or Electro Static Discharge (ESD).

- If a pin is damaged, but not failing (indicated by higher than normal leakage currrent).

- IDD power supply current failures.

- Lower IDD power supply currents could indicate a low power version of the part is being substituted for a higher power version & vice versa.

## What is AC Testing?

#### Table 38: AC Electrical Characteristics (1 of 2) $T_A = -40^{\circ}$ C to +85°C, V<sub>DD</sub> = 2.7-3.6V@33MHz, 4.5-5.5V@40MHz, V<sub>SS</sub> = 0V

|                     |                                   |            |                                              |            | Oscilla                                       | ator                                                               |                              |       |

|---------------------|-----------------------------------|------------|----------------------------------------------|------------|-----------------------------------------------|--------------------------------------------------------------------|------------------------------|-------|

|                     |                                   | Mc<br>16 M | Hz (x1<br>ode)<br>Hz (x2<br>de) <sup>1</sup> | Mc<br>20 M | Hz (x1<br>ode)<br>Hz (x2<br>ode) <sup>1</sup> | Vari                                                               | iable                        |       |

| Symbol              | Parameter                         | Min        | Max                                          | Min        | Max                                           | Min                                                                | Max                          | Units |

| 1/T <sub>CLCL</sub> | x1 Mode Oscillator Fre-<br>quency | 0          | 33                                           | 0          | 40                                            | 0                                                                  | 40                           | MHz   |

| 1/2Talal            | x2 Mode Oscillator Fre-<br>quency | 0          | 16                                           | 0          | 20                                            | 0                                                                  | 20                           | MHz   |

| TLHLL               | ALE Pulse Width                   | 46         |                                              | 35         |                                               | 2T <sub>CLCL</sub> - 15                                            |                              | ns    |

| TAVLL               | Address Valid to ALE Low          | 5          |                                              |            |                                               | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |

|                     |                                   |            |                                              | 10         |                                               | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |

| TLLAX               | Address Hold After ALE<br>Low     | 5          |                                              |            |                                               | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |

|                     |                                   |            |                                              | 10         |                                               | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |

| TLLIV               | ALE Low to Valid Instr In         |            | 56                                           |            |                                               |                                                                    | 4T <sub>CLCL</sub> - 65 (3V) | ns    |

|                     |                                   |            |                                              |            | 55                                            |                                                                    | 4T <sub>CLCL</sub> - 45 (5V) | ns    |

| TLLPL               | ALE Low to PSEN# Low              | 5          |                                              |            |                                               | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |

|                     |                                   |            |                                              | 10         |                                               | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |

| TPLPH               | PSEN# Pulse Width                 | 66         |                                              | 60         |                                               | 3T <sub>CLCL</sub> - 25<br>(3V)<br>3T <sub>CLCL</sub> - 15<br>(5V) |                              | ns    |

| TPLIV               | PSEN# Low to Valid Instr<br>In    |            | 35                                           |            |                                               |                                                                    | 3T <sub>CLCL</sub> - 55 (3V) | ns    |

|                     |                                   |            |                                              |            | 25                                            |                                                                    | 3T <sub>CLCL</sub> - 50 (5V) | ns    |

| TPXIX               | Input Instr Hold After<br>PSEN#   |            |                                              |            |                                               | 0                                                                  |                              | ns    |

| T <sub>PXIZ</sub>   | Input Instr Float After<br>PSEN#  |            | 25                                           |            |                                               |                                                                    | T <sub>OLOL</sub> - 5 (3V)   | ns    |

|                     |                                   |            |                                              |            | 10                                            |                                                                    | T <sub>CLCL</sub> - 15 (5V)  | ns    |

| TPXAV               | PSEN# to Address valid            | 22         |                                              | 17         |                                               | TCLCL - 8                                                          |                              | ns    |

| TAVIV               | Address to Valid Instr In         |            | 72                                           |            |                                               |                                                                    | 5T <sub>CLCL</sub> - 80 (3V) | ns    |

|                     |                                   |            |                                              |            | 65                                            |                                                                    | 5T <sub>CLCL</sub> - 60 (5V) | ns    |

| TPLAZ               | PSEN# Low to Address<br>Float     |            | 10                                           |            | 10                                            |                                                                    | 10                           | ns    |

| T <sub>RLRH</sub>   | RD# Pulse Width                   | 142        |                                              | 120        |                                               | 6T <sub>CLCL</sub> - 40 (3V)<br>6T <sub>CLCL</sub> - 30 (5V)       |                              | ns    |

| TWLWH               | Write Pulse Width (WE#)           | 142        |                                              | 120        |                                               | 6T <sub>CLCL</sub> - 40 (3V)<br>6T <sub>CLCL</sub> - 30 (5V)       |                              | ns    |

| TRLDV               | RD# Low to Valid Data In          |            | 62                                           |            |                                               |                                                                    | 5T <sub>CLCL</sub> - 90 (3V) | ns    |

## **Example AC Parametrics Table:**

|        |                                                |            |                                               |            | Oscilla                                     | ator                                                         |                              |       |

|--------|------------------------------------------------|------------|-----------------------------------------------|------------|---------------------------------------------|--------------------------------------------------------------|------------------------------|-------|

|        |                                                | Mo<br>16 M | Hz (x1<br>ode)<br>Hz (x2<br>ode) <sup>1</sup> | Mc<br>20 M | Hz (x1<br>de)<br>Hz (x2<br>de) <sup>1</sup> | Vari                                                         | iable                        |       |

| Symbol | Parameter                                      | Min        | Max                                           | Min        | Max                                         | Min                                                          | Max                          | Units |

|        |                                                |            |                                               |            | 75                                          |                                                              | 5T <sub>CLCL</sub> - 50 (5V) | ns    |

| TRHDX  | Data Hold After RD#                            | 0          |                                               | 0          |                                             | 0                                                            |                              | ns    |

| TRHDZ  | Data Float After RD#                           |            | 36                                            |            |                                             |                                                              | 2Talal - 25 (3V)             | ns    |

|        |                                                |            |                                               |            | 38                                          |                                                              | 2Talal - 12 (5V)             | ns    |

| TLLDV  | ALE Low to Valid Data In                       |            | 152                                           |            |                                             |                                                              | 8Touce - 90 (3V)             | ns    |

|        | 1                                              |            |                                               |            | 150                                         |                                                              | 8Touce - 50 (5V)             | ns    |

| TAVDV  | Address to Valid Data In                       |            | 183                                           |            |                                             |                                                              | 9TcLcL - 90 (3V)             | ns    |

|        |                                                |            |                                               |            | 150                                         |                                                              | 9ToLoL - 75 (5V)             | ns    |

| TLLWL  | ALE Low to RD# or WR#<br>Low                   | 66         | 116                                           | 60         | 90                                          | 3T <sub>CLCL</sub> - 25 (3V)<br>3T <sub>CLCL</sub> - 15 (5V) |                              | ns    |

| TAVWL  | Address to RD# or WR#<br>Low                   | 46         |                                               |            |                                             | 4T <sub>CLCL</sub> - 75 (3V)                                 |                              | ns    |

|        | 1                                              |            |                                               | 70         |                                             | 4T <sub>CLCL</sub> - 30 (5V)                                 |                              | ns    |

| TWHOX  | Data Hold After WR#                            | 3          |                                               |            |                                             | T <sub>CLCL</sub> - 27 (3V)                                  |                              | ns    |

|        | 1                                              |            |                                               | 5          |                                             | T <sub>CLCL</sub> - 20 (5V)                                  |                              | ns    |

| Таумн  | Data Valid to WR# High                         | 142        |                                               |            |                                             | 7T <sub>CLCL</sub> - 70 (3V)                                 |                              | ns    |

|        | 1                                              |            |                                               | 125        |                                             | 7T <sub>CLCL</sub> - 50 (5V)                                 |                              | ns    |

| TQVWX  | Data Valid to WR# High to<br>Low<br>Transition | 10         |                                               | 5          |                                             | T <sub>CLCL</sub> - 20                                       |                              | ns    |

| TRLAZ  | RD# Low to Address Float                       |            | 0                                             |            | 0                                           |                                                              | 0                            | ns    |

| TWHLH  | RD# to WR# High to ALE<br>High                 | 5          | 55                                            |            |                                             | T <sub>CLCL</sub> - 25 (3V)                                  | T <sub>CLCL</sub> + 25 (3V)  | ns    |

|        | 1 1                                            |            |                                               | 10         | 40                                          | ToloL - 15 (5V)                                              | TCLCL + 15 (5V)              | ns    |

1. Calculated values are for x1 Mode only

T0-0.0 25093

Source: Microchip FlashFlex MCU Datasheet, 02/13

AC testing will tell you the speed at which things happen in the device like:

- How long does it take to access an address (access time).

- How long does it take for one signal occur after another (prop. delay).

- Maximum operating frequency.

- Signal rise and fall times.

But AC testing by itself, while better than just DC testing, still only tests a small percentage of the die at any one time.

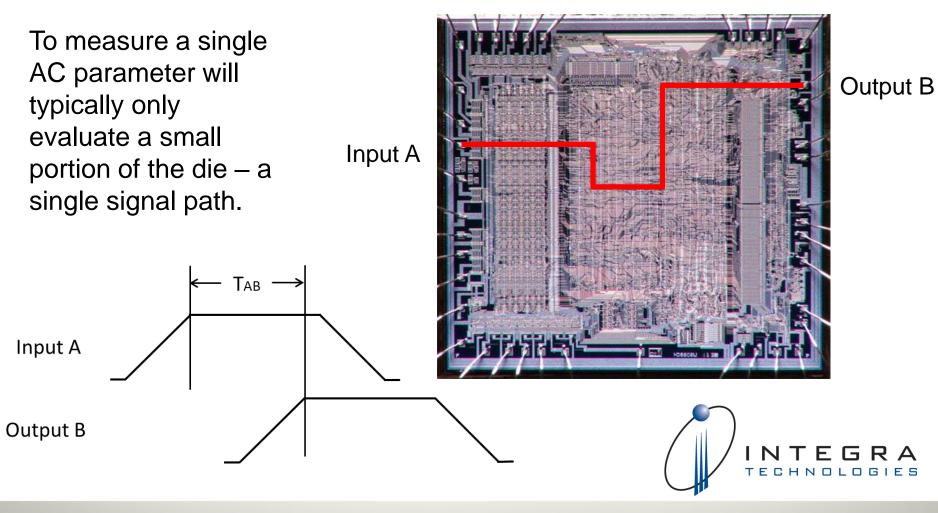

## What is AC Testing?

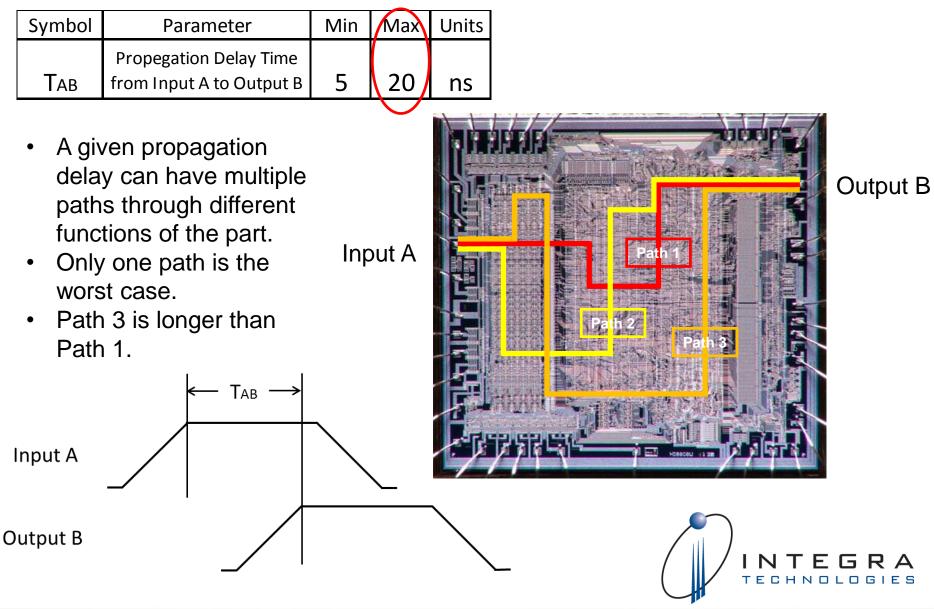

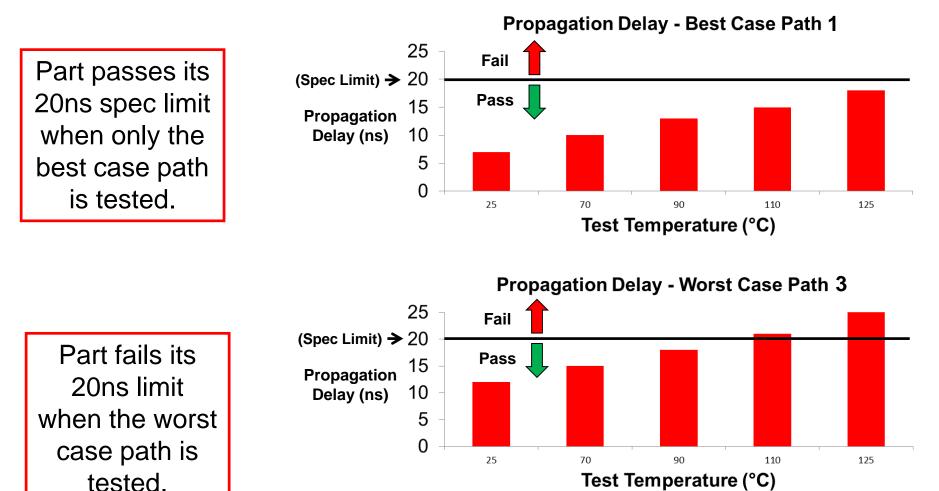

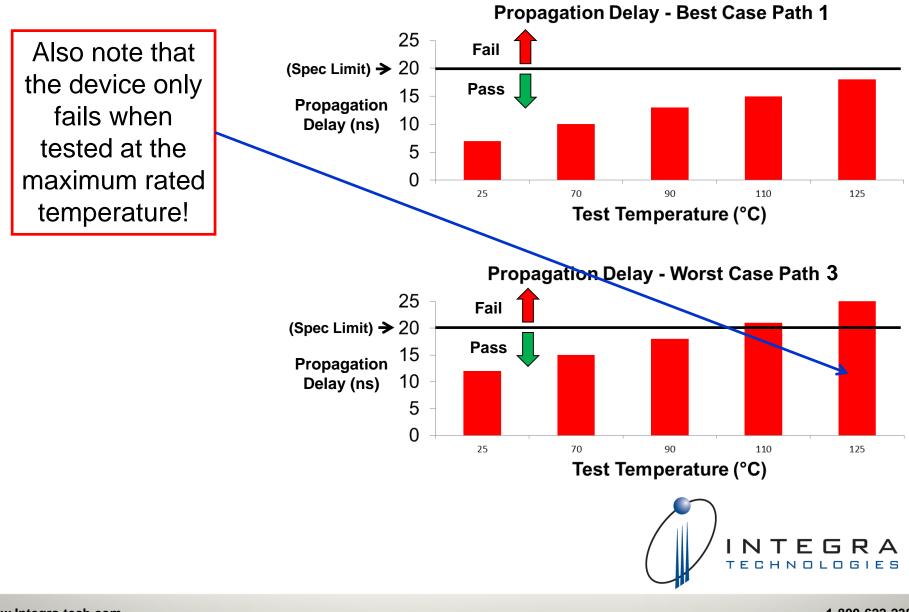

## **Propagation Delay Example**

| Symbol | Parameter                | Min | Max | Units |

|--------|--------------------------|-----|-----|-------|

|        | Propegation Delay Time   |     |     |       |

| Тав    | from Input A to Output B | 5   | 20  | ns    |

## What is AC Testing?

## **Propagation Delay Example**

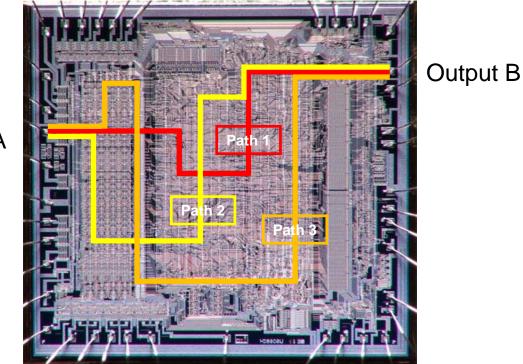

There may be several 100's or 1000's of paths through a device that are represented by a single AC parameter. The value listed in the datasheet is Input A the worst case of all those paths. So each path needs to be evaluated to determine if they all work.

In this case there are 3 paths from Input A to Output B. Path 3 is clearly the longest and is likely the worst case propagation delay path for this AC parameter.

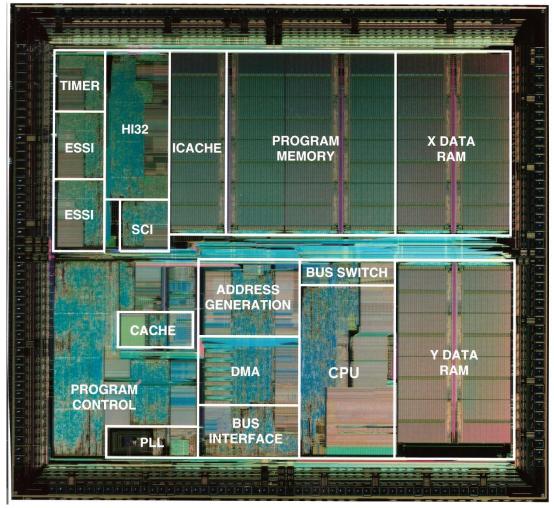

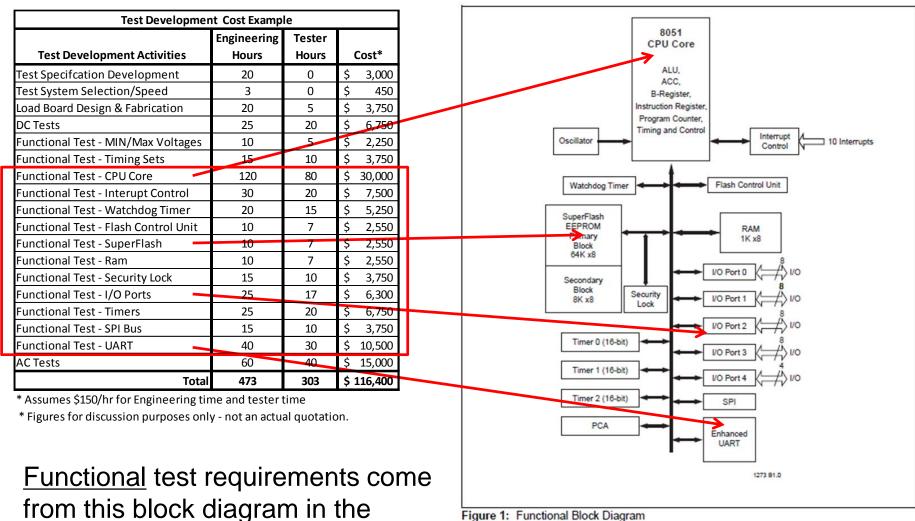

- Functional testing is making sure that all of the functions that a device can perform are exercised.

- Ironically it is usually the area of the device that is the least explained in the datasheet.

- The development of the functional test area of a complex parts accounts for 50% to 90% of the overall test development effort – and therefore the test development cost.

- Circling datasheet limits does not specify any functional tests for complex parts. It may be an adequate means of specifying tests for simple parts like Transistors and Op Amps, but it is not an adequate method for specifying testing of complex parts.

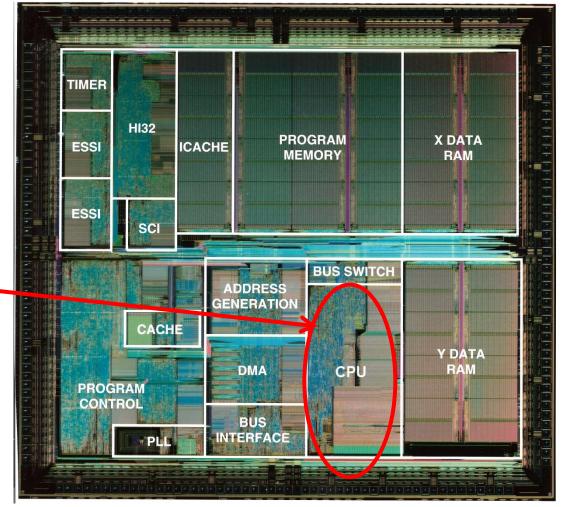

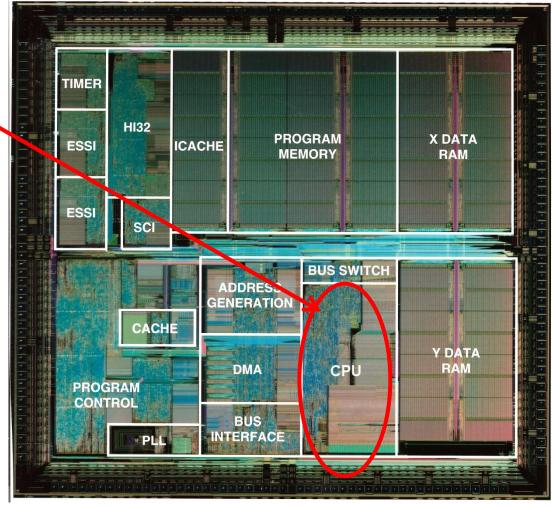

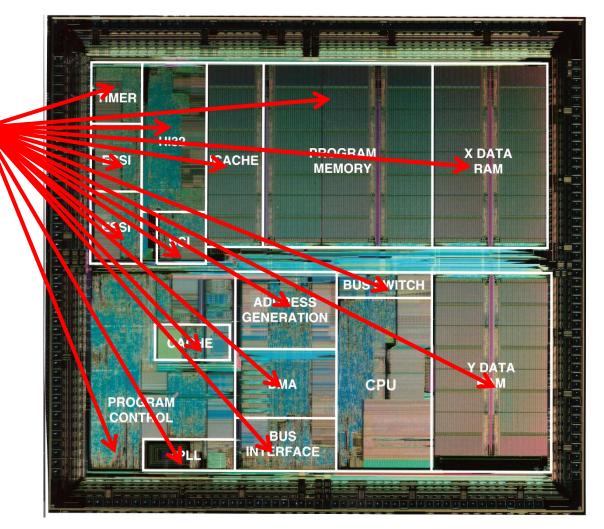

Functional testing requires that each functional block in a device be thoroughly tested.

This is where up to 90% of the test development effort lies when doing a complex part.

Each white named area is a functional block for this device.

As an example, lets see what it might take to develop a functional test just the Central Processing Unit (CPU) on this microcontroller.

## **CPU Functional Tests**

- ~112 different instructions

- 6 addressing modes

- 27 Registers

- 5 I/O Ports

- 8 bit data values = 256 possible data values

- All multiplied together

| Instructions     | # Types | # Data Values | # tests required to<br>fully test |  |

|------------------|---------|---------------|-----------------------------------|--|

| Data Transfer    | 29      | 256           | 7,424                             |  |

| Arithmetic       | 24      | 256           | 6,144                             |  |

| Logical          | 25      | 256           | 6,400                             |  |

| Bit Manipulation | 12      | 256           | 3,072                             |  |

| Program Control  | 22      | 256           | 5,632                             |  |

|                  | 112     |               | 28,672                            |  |

|                  |         |               |                                   |  |

| Addressing Modes | 6       |               | 172,032                           |  |

|                  |         |               |                                   |  |

| Registers        | 27      |               | 4,644,864                         |  |

|                  |         |               |                                   |  |

| #I/O Ports       | 5       |               | 23,224,320                        |  |

|                  |         |               |                                   |  |

| MIM/MAX Voltage  | 2       |               | 46,448,640                        |  |

|                  |         |               |                                   |  |

| -55C, 25C +125C  | 3       |               | 139,345,920                       |  |

The number of functional tests required to fully test the CPU is the result of multiplying the number of instruction types times the # of possible data values times the # addressing modes, etc.

Table Source: http://www.alciro.org/alciro/microcontroladores-8051\_24/ tipos-instrucciones-microcontroladores-8051\_284\_en.htm

## **CPU Functional Tests**

- ~112 different instructions

- 6 addressing modes

- 27 Registers

- 5 I/O Ports

- 8 bit data values = 256 possible data values

- All multiplied together

| Instructions     | # Types | # Data Values | # tests required to<br>fully test |

|------------------|---------|---------------|-----------------------------------|

| Data Transfer    | 29      | 256           | 7,424                             |

| Arithmetic       | 24      | 256           | 6,144                             |

| Logical          | 25      | 256           | 6,400                             |

| Bit Manipulation | 12      | 256           | 3,072                             |

| Program Control  | 22      | 256           | 5,632                             |

|                  | 112     |               | 28,672                            |

| Addressing Modes | 6       |               | 172,032                           |

| Registers        | 27      |               | 4,644,864                         |

| #I/O Ports       | 5       |               | 23,224,320                        |

| MIM/MAX Voltage  | 2       |               | 46,448,640                        |

| -55C, 25C +125C  | 3       |               | 139,345,920                       |

- The number of functional tests required to fully test the CPU is the result of multiplying the number of instruction types times the # of possible data values times the # addressing modes, etc.

- In this case that's over 23,000,000 functional tests.

Table Source: http://www.alciro.org/alciro/microcontroladores-8051\_24/ tipos-instrucciones-microcontroladores-8051\_284\_en.htm

## **CPU Functional Tests**

- ~112 different instructions

- 6 addressing modes

- 27 Registers

- 5 I/O Ports

- 8 bit data values = 256 possible data values

- All multiplied together

- Then times 2 voltages

- Then times 3 temperatures

| Instructions     | # Types | # Data Values | # tests required to<br>fully test |

|------------------|---------|---------------|-----------------------------------|

| Data Transfer    | 29      | 256           | 7,424                             |

| Arithmetic       | 24      | 256           | 6,144                             |

| Logical          | 25      | 256           | 6,400                             |

| Bit Manipulation | 12      | 256           | 3,072                             |

| Program Control  | 22      | 256           | 5,632                             |

|                  | 112     |               | 28,672                            |

| Addressing Modes | 6       |               | 172,032                           |

| Registers        | 27      |               | 4,644,864                         |

| #I/O Ports       | 5       |               | 23,224,320                        |

| WIIM/MAX Voltage | 2       |               | 46,448,640                        |

| -55C, 25C +125C  | 3       |               | 139,345,920                       |

When those 23 million functional tests are run at 2 voltages and then at 3 temperatures, the resulting number now equals ~140,000,000 functional tests!

Table Source: http://www.alciro.org/alciro/microcontroladores-8051\_24/ tipos-instrucciones-microcontroladores-8051\_284\_en.htm

And those 140 million tests just covers the CPU

portion of the device.

- A similar approach must be taken for each of the other 16 functional blocks in this device.

- This can make functional testing very time consuming and very expensive.

- What can happen if all functional blocks are not tested?

What can happen if all functional blocks are not tested

• What can happen if all functional blocks are not tested

G

N

CHNOLO

• What can happen if all functional blocks are not tested

## **Important Functional Testing Points:**

- Functional testing is the most important part of developing a test program for complex parts.

- Yet it is often not specified in test requirements and simply left to the test lab to decide upon.

- When Functional Testing requirements are not specified, you can't be sure if your after-market purchased part will function correctly in your application.

- When Functional Testing requirements are not specified, it makes cost comparisons between test lab quotations very difficult - or even impossible.

| Test Developmer                      | nt Cost Examp        | le              |            |

|--------------------------------------|----------------------|-----------------|------------|

| Test Development Activities          | Engineering<br>Hours | Tester<br>Hours | Cost*      |

| Test Specifcation Development        | 20                   | 0               | \$ 3,000   |

| Test System Selection/Speed          | 3                    | 0               | \$ 450     |

| Load Board Design & Fabrication      | 20                   | 5               | \$ 3,750   |

| DC Tests                             | 25                   | 20              | \$ 6,750   |

| Functional Test - MIN/Max Voltages   | 10                   | 5               | \$ 2,250   |

| Functional Test - Timing Sets        | 15                   | 10              | \$ 3,750   |

| Functional Test - CPU Core           | 120                  | 80              | \$ 30,000  |

| Functional Test - Interupt Control   | 30                   | 20              | \$ 7,500   |

| Functional Test - Watchdog Timer     | 20                   | 15              | \$ 5,250   |

| Functional Test - Flash Control Unit | 10                   | 7               | \$ 2,550   |

| Functional Test - SuperFlash         | 10                   | 7               | \$ 2,550   |

| Functional Test - Ram                | 10                   | 7               | \$ 2,550   |

| Functional Test - Security Lock      | 15                   | 10              | \$ 3,750   |

| Functional Test - I/O Ports          | 25                   | 17              | \$ 6,300   |

| Functional Test - Timers             | 25                   | 20              | \$ 6,750   |

| Functional Test - SPI Bus            | 15                   | 10              | \$ 3,750   |

| Functional Test - UART               | 40                   | 30              | \$ 10,500  |

| AC Tests                             | 60                   | 40              | \$ 15,000  |

| Total                                | 473                  | 303             | \$ 116,400 |

Comprehensive Test Program Development Quotation Example

This is how your test lab should be quoting your project.

\* Assumes \$150/hr for Engineering time and tester time

\* Figures for discussion purposes only - not an actual quotation.

| Test Developmer                      | nt Cost Examp | le     |            |

|--------------------------------------|---------------|--------|------------|

|                                      | Engineering   | Tester |            |

| Test Development Activities          | Hours         | Hours  | Cost*      |

| Test Specifcation Development        | 20            | 0      | \$ 3,000   |

| Test System Selection/Speed          | 3             | 0      | \$ 450     |

| Load Board Design & Fabrication      | 20            | 5      | \$ 3,750   |

| DC Tests                             | 25            | 20     | \$ 6,750   |

| Functional Test - MIN/Max Voltages   | 10            | 5      | \$ 2,250   |

| Functional Test - Timing Sets        | 15            | 10     | \$ 3,750   |

| Functional Test - CPU Core           | 120           | 80     | \$ 30,000  |

| Functional Test - Interupt Control   | 30            | 20     | \$ 7,500   |

| Functional Test - Watchdog Timer     | 20            | 15     | \$ 5,250   |

| Functional Test - Flash Control Unit | 10            | 7      | \$ 2,550   |

| Functional Test - SuperFlash         | 10            | 7      | \$ 2,550   |

| Functional Test - Ram                | 10            | 7      | \$ 2,550   |

| Functional Test - Security Lock      | 15            | 10     | \$ 3,750   |

| Functional Test - I/O Ports          | 25            | 17     | \$ 6,300   |

| Functional Test - Timers             | 25            | 20     | \$ 6,750   |

| Functional Test - SPI Bus            | 15            | 10     | \$ 3,750   |

| Functional Test - UART               | 40            | 30     | \$ 10,500  |

| AC Tests                             | 60            | 40     | \$ 15,000  |

| Total                                | 473           | 303    | \$ 116,400 |

\* Assumes \$150/hr for Engineering time and tester time

\* Figures for discussion purposes only - not an actual quotation.

# <u>DC</u> test requirements come from this table in the datasheet.

#### **DC Electrical Characteristics**

Table 36: DC Electrical Characteristics for SST89E516RDx  $T_A = -40^{\circ}$ C to +85°C;  $V_{DD} = 4.5-5.5V$ ;  $V_{SS} = 0V$

| Symbol           | Parameter                                                      | Test Conditions                               | Min                         | Max                         | Units |

|------------------|----------------------------------------------------------------|-----------------------------------------------|-----------------------------|-----------------------------|-------|

| VIL              | Input Low Voltage                                              | 4.5 < V <sub>DD</sub> < 5.5                   | -0.5                        | 0.2V <sub>DD</sub> -<br>0.1 | v     |

| VIH              | Input High Voltage                                             | 4.5 < V <sub>DD</sub> < 5.5                   | 0.2V <sub>DD</sub> +<br>0.9 | V <sub>DD</sub> + 0.5       | v     |

| VIH1             | Input High Voltage (XTAL1, RST)                                | 4.5 < V <sub>DD</sub> < 5.5                   | 0.7Vpp                      | V <sub>DD</sub> + 0.5       | V     |

| Vol              | L Output Low Voltage (Ports 1.5, 1.6, 1.7)                     | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  |                                                                | IoL = 16mA                                    |                             | 1.0                         | V     |

| Vol              | VoL Output Low Voltage (Ports 1, 2, 3) <sup>1</sup>            | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  |                                                                | loL = 100μA <sup>2</sup>                      |                             | 0.3                         | V     |

|                  |                                                                | IoL = 1.6mA <sup>2</sup>                      |                             | 0.45                        | V     |

|                  |                                                                | IoL = 3.5mA <sup>2</sup>                      |                             | 1.0                         | V     |

| V <sub>OL1</sub> | Output Low Voltage (Port 0, ALE,                               | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  | PSEN#) <sup>1,3</sup>                                          | I <sub>OL</sub> = 200μA <sup>2</sup>          |                             | 0.3                         | V     |

|                  | I <sub>OL</sub> = 3.2r                                         | $I_{OL} = 3.2 m A^2$                          |                             | 0.45                        | V     |

| VOH              | Output High Voltage (Ports 1, 2, 3, ALE,                       | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  | PSEN#) <sup>4</sup>                                            | l <sub>OH</sub> = -10μA                       | V <sub>DD</sub> - 0.3       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -30µА                       | V <sub>DD</sub> - 0.7       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -60µА                       | V <sub>DD</sub> - 1.5       |                             | V     |

| V <sub>OH1</sub> | Output High Voltage (Port 0 in External                        | V <sub>DD</sub> = 4.5V                        |                             |                             |       |

|                  | Bus Mode) <sup>4</sup>                                         | I <sub>OH</sub> = -200µА                      | V <sub>DD</sub> - 0.3       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -3.2mA                      | V <sub>DD</sub> - 0.7       |                             | V     |

| VBOD             | Brown-out Detection Voltage                                    |                                               | 3.85                        | 4.15                        | V     |

| Ι <sub>ΙL</sub>  | Logical 0 Input Current (Ports 1, 2, 3)                        | V <sub>IN</sub> = 0.4V                        |                             | -75                         | μA    |

| ITL              | Logical 1-to-0 Transition Current (Ports 1, 2, 3) <sup>5</sup> | V <sub>IN</sub> = 2V                          |                             | -650                        | μA    |

| I <sub>LI</sub>  | Input Leakage Current (Port 0)                                 | 0.45 < V <sub>IN</sub> < V <sub>DD</sub> -0.3 |                             | ±10                         | μA    |

| R <sub>RST</sub> | RST Pull-down Resistor                                         |                                               | 40                          | 225                         | KΩ    |

| CIO              | Pin Capacitance <sup>6</sup>                                   | @ 1 MHz, 25°C                                 |                             | 15                          | pF    |

| IDD              | Power Supply Current                                           |                                               |                             |                             |       |

|                  | IAP Mode                                                       |                                               |                             |                             |       |

|                  | @ 40 MHz                                                       |                                               |                             | 88                          | mA    |

|                  | Active Mode                                                    |                                               |                             |                             |       |

|                  | @ 40 MHz                                                       |                                               |                             | 50                          | mA    |

|                  | Idle Mode                                                      |                                               |                             |                             |       |

|                  | @ 40 MHz                                                       |                                               |                             | 42                          | mA    |

|                  | Power-down Mode (min. Vpp = 2V)                                | T <sub>A</sub> = 0°C to +70°C                 |                             | 80                          | μA    |

| 1                |                                                                |                                               |                             |                             |       |

Source: Microchip FlashFlex MCU Datasheet, 02/13

| Test Developmer                      | nt Cost Examp        | le              |            |

|--------------------------------------|----------------------|-----------------|------------|

| Test Development Activities          | Engineering<br>Hours | Tester<br>Hours | Cost*      |

| Test Specifcation Development        | 20                   | 0               | \$ 3,000   |

| Test System Selection/Speed          | 3                    | 0               | \$ 450     |

| Load Board Design & Fabrication      | 20                   | 5               | \$ 3,750   |

| DC Tests                             | 25                   | 20              | \$ 6,750   |

| Functional Test - MIN/Max Voltages   | 10                   | 5               | \$ 2,250   |

| Functional Test - Timing Sets        | 15                   | 10              | \$ 3,750   |

| Functional Test - CPU Core           | 120                  | 80              | \$ 30,000  |

| Functional Test - Interupt Control   | 30                   | 20              | \$ 7,500   |

| Functional Test - Watchdog Timer     | 20                   | 15              | \$ 5,250   |

| Functional Test - Flash Control Unit | 10                   | 7               | \$ 2,550   |

| Functional Test - SuperFlash         | 10                   | 7               | \$ 2,550   |

| Functional Test - Ram                | 10                   | 7               | \$ 2,550   |

| Functional Test - Security Lock      | 15                   | 10              | \$ 3,750   |

| Functional Test - I/O Ports          | 25                   | 17              | \$ 6,300   |

| Functional Test - Timers             | 25                   | 20              | \$ 6,750   |

| Functional Test - SPI Bus            | 15                   | 10              | \$ 3,750   |

| Functional Test - UART               | 40                   | 30              | \$ 10,500  |

| AC Tests                             | 60                   | 40              | \$ 15,000  |

| Total                                | 473                  | 303             | \$ 116,400 |

\* Assumes \$150/hr for Engineering time and tester time

\* Figures for discussion purposes only - not an actual quotation.

# <u>AC</u> test requirements come from this table in the datasheet.

|                     |                                   |            |                                               | -          |                                               | -                                                                  |                              |       |

|---------------------|-----------------------------------|------------|-----------------------------------------------|------------|-----------------------------------------------|--------------------------------------------------------------------|------------------------------|-------|

|                     |                                   |            |                                               |            | Oscilla                                       | itor                                                               |                              |       |

|                     |                                   | Mo<br>16 M | Hz (x1<br>ode)<br>Hz (x2<br>ode) <sup>1</sup> | Mc<br>20 M | Hz (x1<br>ode)<br>Hz (x2<br>ode) <sup>1</sup> | Vari                                                               | iable                        |       |

| Symbol              | Parameter                         | Min        | Max                                           | Min        | Max                                           | Min                                                                | Max                          | Units |

| 1/T <sub>CLCL</sub> | x1 Mode Oscillator Fre-<br>quency | 0          | 33                                            | 0          | 40                                            | 0                                                                  | 40                           | MHz   |

| 1/2Talal            | x2 Mode Oscillator Fre-<br>quency | 0          | 16                                            | 0          | 20                                            | 0                                                                  | 20                           | MHz   |

| TLHLL               | ALE Pulse Width                   | 46         |                                               | 35         |                                               | 2T <sub>CLCL</sub> - 15                                            |                              | ns    |

| TAVLL               | Address Valid to ALE Low          | 5          |                                               |            |                                               | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |

|                     |                                   |            |                                               | 10         |                                               | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |

| TLLAX               | Address Hold After ALE<br>Low     | 5          |                                               |            |                                               | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |

|                     |                                   |            |                                               | 10         |                                               | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |

| TLLIV               | ALE Low to Valid Instr In         |            | 56                                            |            |                                               |                                                                    | 4T <sub>CLCL</sub> - 65 (3V) | ns    |

|                     |                                   |            |                                               |            | 55                                            |                                                                    | 4T <sub>CLCL</sub> - 45 (5V) | ns    |

| TLLPL               | ALE Low to PSEN# Low              | 5          |                                               |            |                                               | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |

|                     |                                   |            |                                               | 10         |                                               | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |

| TPLPH               | PSEN# Pulse Width                 | 66         |                                               | 60         |                                               | 3T <sub>CLCL</sub> - 25<br>(3V)<br>3T <sub>CLCL</sub> - 15<br>(5V) |                              | ns    |

| TPLIV               | PSEN# Low to Valid Instr<br>In    |            | 35                                            |            |                                               |                                                                    | 3T <sub>CLCL</sub> - 55 (3V) | ns    |

|                     |                                   |            |                                               |            | 25                                            |                                                                    | 3T <sub>CLCL</sub> - 50 (5V) | ns    |

| TPXIX               | Input Instr Hold After<br>PSEN#   |            |                                               |            |                                               | 0                                                                  |                              | ns    |

| T <sub>PXIZ</sub>   | Input Instr Float After<br>PSEN#  |            | 25                                            |            |                                               |                                                                    | T <sub>CLCL</sub> - 5 (3V)   | ns    |

|                     |                                   |            |                                               |            | 10                                            |                                                                    | T <sub>CLCL</sub> - 15 (5V)  | ns    |

| TPXAV               | PSEN# to Address valid            | 22         |                                               | 17         |                                               | TCLCL - 8                                                          |                              | ns    |

| TAVIV               | Address to Valid Instr In         |            | 72                                            |            |                                               |                                                                    | 5T <sub>CLCL</sub> - 80 (3V) | ns    |

|                     |                                   |            |                                               |            | 65                                            |                                                                    | 5T <sub>CLCL</sub> - 60 (5V) | ns    |

| TPLAZ               | PSEN# Low to Address<br>Float     |            | 10                                            |            | 10                                            |                                                                    | 10                           | ns    |

| T <sub>RLRH</sub>   | RD# Pulse Width                   | 142        |                                               | 120        |                                               | 6T <sub>CLCL</sub> - 40 (3V)<br>6T <sub>CLCL</sub> - 30 (5V)       |                              | ns    |

| TWLWH               | Write Pulse Width (WE#)           | 142        |                                               | 120        |                                               | 6T <sub>CLCL</sub> - 40 (3V)<br>6T <sub>CLCL</sub> - 30 (5V)       |                              | ns    |

| TRLDV               | RD# Low to Valid Data In          |            | 62                                            |            |                                               |                                                                    | 5T <sub>CLCL</sub> - 90 (3V) | ns    |

Source: Microchip FlashFlex MCU Datasheet, 02/13

Source: Microchip FlashFlex MCU Datasheet, 02/13

datasheet and a separate

programming guide.

| Test Development Cost Example        |                      |                 |            |  |  |  |  |

|--------------------------------------|----------------------|-----------------|------------|--|--|--|--|

| Test Development Activities          | Engineering<br>Hours | Tester<br>Hours | Cost*      |  |  |  |  |

| Test Specifcation Development        | 20                   | 0               | \$ 3,000   |  |  |  |  |

| Test System Selection/Speed          | 3                    | 0               | \$ 450     |  |  |  |  |

| Load Board Design & Fabrication      | 20                   | 5               | \$ 3,750   |  |  |  |  |

| DC Tests                             | 25                   | 20              | \$ 6,750   |  |  |  |  |

| Functional Test - MIN/Max Voltages   | 10                   | 5               | \$ 2,250   |  |  |  |  |

| Functional Test - Timing Sets        | 15                   | 10              | \$ 3,750   |  |  |  |  |

| Functional Test - CPU Core           | 120                  | 80              | \$ 30,000  |  |  |  |  |

| Functional Test - Interupt Control   | 30                   | 20              | \$ 7,500   |  |  |  |  |

| Functional Test - Watchdog Timer     | 20                   | 15              | \$ 5,250   |  |  |  |  |

| Functional Test - Flash Control Unit | 10                   | 7               | \$ 2,550   |  |  |  |  |

| Functional Test - SuperFlash         | 10                   | 7               | \$ 2,550   |  |  |  |  |

| Functional Test - Ram                | 10                   | 7               | \$ 2,550   |  |  |  |  |

| Functional Test - Security Lock      | 15                   | 10              | \$ 3,750   |  |  |  |  |

| Functional Test - I/O Ports          | 25                   | 17              | \$ 6,300   |  |  |  |  |

| Functional Test - Timers             | 25                   | 20              | \$ 6,750   |  |  |  |  |

| Functional Test - SPI Bus            | 15                   | 10              | \$ 3,750   |  |  |  |  |

| Functional Test - UART               | 40                   | 30              | \$ 10,500  |  |  |  |  |

| AC Tests                             | 60                   | 40              | \$ 15,000  |  |  |  |  |

| Total                                | 473                  | 303             | \$ 116,400 |  |  |  |  |

\* Assumes \$150/hr for Engineering time and tester time

\* Figures for discussion purposes only - not an actual quotation.

|   | Test Development Percentage Effort      |                      |                 |          |  |  |

|---|-----------------------------------------|----------------------|-----------------|----------|--|--|

|   | Test Development Activities             | Engineering<br>Hours | Tester<br>Hours | % Effort |  |  |

|   | · · · · · · · · · · · · · · · · · · ·   |                      | 5               |          |  |  |

|   | Misc Test Development Items<br>DC Tests | 43                   | 20              | 9%<br>5% |  |  |

| < | Eunctional Tests                        | 345                  | 238             | 73%      |  |  |

|   | AC Tests                                | 60                   | 40              | 13%      |  |  |

|   | Total                                   | 473                  | 303             | 100%     |  |  |

73% of effort/cost is in functional test development

Figure 1: Functional Block Diagram

Source: Microchip FlashFlex MCU Datasheet, 02/13

| Test Development Cost Example        |                      |                 |            |  |  |  |  |

|--------------------------------------|----------------------|-----------------|------------|--|--|--|--|

| Test Development Activities          | Engineering<br>Hours | Tester<br>Hours | Cost*      |  |  |  |  |

| Test Specifcation Development 🥏      | 20                   | 0               | \$ 3,000   |  |  |  |  |

| Test System Selection/Speed          | 3                    | 0               | \$ 450     |  |  |  |  |

| Load Board Design & Fabrication      | 20                   | 5               | \$ 3,750   |  |  |  |  |

| DC Tests                             | 25                   | 20              | \$ 6,750   |  |  |  |  |

| Functional Test - MIN/Max Voltages   | 10                   | 5               | \$ 2,250   |  |  |  |  |

| Functional Test - Timing Sets        | 15                   | 10              | \$ 3,750   |  |  |  |  |

| Functional Test - CPU Core           | 120                  | 80              | \$ 30,000  |  |  |  |  |

| Functional Test - Interupt Control   | 30                   | 20              | \$ 7,500   |  |  |  |  |

| Functional Test - Watchdog Timer     | 20                   | 15              | \$ 5,250   |  |  |  |  |

| Functional Test - Flash Control Unit | 10                   | 7               | \$ 2,550   |  |  |  |  |

| Functional Test - SuperFlash         | 10                   | 7               | \$ 2,550   |  |  |  |  |

| Functional Test - Ram                | 10                   | 7               | \$ 2,550   |  |  |  |  |

| Functional Test - Security Lock      | 15                   | 10              | \$ 3,750   |  |  |  |  |

| Functional Test - I/O Ports          | 25                   | 17              | \$ 6,300   |  |  |  |  |

| Functional Test - Timers             | 25                   | 20              | \$ 6,750   |  |  |  |  |

| Functional Test - SPI Bus            | 15                   | 10              | \$ 3,750   |  |  |  |  |

| Functional Test - UART               | 40                   | 30              | \$ 10,500  |  |  |  |  |

| AC Tests                             | 60                   | 40              | \$ 15,000  |  |  |  |  |

| Total                                | 473                  | 303             | \$ 116,400 |  |  |  |  |

#### The Test Specification is critical

- Clearly defining exactly what tests need to be done and under what conditions will assure that an adequate test is performed.

- The test specification can also help reduce costs by not testing functions that are not important to the application – this will be discussed more later.

\* Assumes \$150/hr for Engineering time and tester time

\* Figures for discussion purposes only - not an actual quotation.

• Spend the time to be clear up front about what tests need to be run and under what conditions – this will assure you get the test you need.

| Test Development Cost Example        |             |        |            |  |  |  |  |

|--------------------------------------|-------------|--------|------------|--|--|--|--|

|                                      | Engineering | Tester |            |  |  |  |  |

| Test Development Activities          | Hours       | Hours  | Cost*      |  |  |  |  |

| Test Specification Development       | 20          | 0      | \$ 3,000   |  |  |  |  |

| Test System Selection/Speed          | 3           | 0      | \$ 450     |  |  |  |  |

| Load Board Design & Fabrication      | 20          | 5      | \$ 3,750   |  |  |  |  |

| DC Tests                             | 25          | 20     | \$ 6,750   |  |  |  |  |

| Functional Test - MIN/Max Voltages   | 10          | 5      | \$ 2,250   |  |  |  |  |

| Functional Test - Timing Sets        | 15          | 10     | \$ 3,750   |  |  |  |  |

| Functional Test - CPU Core           | 120         | 80     | \$ 30,000  |  |  |  |  |

| Functional Test - Interupt Control   | 30          | 20     | \$ 7,500   |  |  |  |  |

| Functional Test - Watchdog Timer     | 20          | 15     | \$ 5,250   |  |  |  |  |

| Functional Test - Flash Control Unit | 10          | 7      | \$ 2,550   |  |  |  |  |

| Functional Test - SuperFlash         | 10          | 7      | \$ 2,550   |  |  |  |  |

| Functional Test - Ram                | 10          | 7      | \$ 2,550   |  |  |  |  |

| Functional Test - Security Lock      | 15          | 10     | \$ 3,750   |  |  |  |  |

| Functional Test - I/O Ports          | 25          | 17     | \$ 6,300   |  |  |  |  |

| Functional Test - Timers             | 25          | 20     | \$ 6,750   |  |  |  |  |

| Functional Test - SPI Bus            | 15          | 10     | \$ 3,750   |  |  |  |  |

| Functional Test - UART               | 40          | 30     | \$ 10,500  |  |  |  |  |

| AC Tests                             | 60          | 40     | \$ 15,000  |  |  |  |  |

| Total                                | 473         | 303    | \$ 116,400 |  |  |  |  |

#### Test System selection is critical

- Test system must be capable of testing at full device speed.

- If you have a 500MHz max operating frequency device, the tester **MUST** be also be capable of testing at 500MHz.

- The hourly rate of the tester is proportional to its performance, so choose the test system that has the lowest performance that can meet the device's performance requirements.

\* Assumes \$150/hr for Engineering time and tester time

\* Figures for discussion purposes only - not an actual quotation.

- Don't settle for a tester with lower performance than your device requires.

- Don't pay for a tester with more performance than you need.

- Be sure the engineer writing the test program has sufficient experience.

## **Saving Test Development Costs**

Since the manufacturer has already thoroughly tested the devices as a part of their original manufacturing flow, the developer is able to limit the counterfeit device testing to match only the actual application conditions.

- 1. Use actual application speeds.

- 2. Use actual application programing code (uP and memory).

- 3. Use actual application designs (FPGA).

- 4. Test only functional blocks actually used in the application.

- 5. Test only the AC parameters that are critical to the application.

- 6. Leverage test programs already developed for the same or similar parts.

- 7. Use device emulators.

- 8. Use golden devices to "learn" device functionality.

## How can test development costs be saved?

| Test Developmer                      | nt Cost Examp        | le              |            | Cost Savings Opportunities                 |                      |                 |           |  |

|--------------------------------------|----------------------|-----------------|------------|--------------------------------------------|----------------------|-----------------|-----------|--|

| Test Development Activities          | Engineering<br>Hours | Tester<br>Hours | Cost       | Description                                | Engineering<br>Hours | Tester<br>Hours | Cost      |  |